Na lição anterior aprendemos como funcionam os principais tipos de flip-flops, verificando que, dependendo dos recursos que cada um possua, podem ser empregados de diversas formas. Também vimos as entradas que estes dispositivos podem conter para melhorar seu desempenho em determinadas aplicações, como por exemplo, nos computadores. Estudamos ainda nas primeiras lições do curso as funções lógicas usadas em diversos circuitos. Tudo isso nos leva à necessidade de contarmos com estas funções na forma de circuitos integrados. De fato, existem muitos circuitos integrados TTL e CMOS contendo flip-flops dos tipos estudados e todas as funções lógicas (portas e inversores e amplificadores) e será justamente deles que falaremos neste artigo.1 - OS FLIP-FLOPS TTL

A família de circuitos integrados digitais TTL conta com uma grande quantidade de flip-flops usados numa infinidade de aplicações práticas.

A diferença de cada tipo de circuito integrado não está apenas no tipo de flip-flop que contém como também nos seus recursos e na sua quantidade. Também devemos observar que um fator importante na escolha de um flip-flop para uma determinada aplicação é a sua velocidade. Para as diversas famílias TTL podemos especificar as máximas velocidades dos seus flip-flops da seguinte maneira:

Standard (74) - 35 MHz

Low Power (74L) - 3 MHz

Low Power Shottky (74LS)

- 45 MHz

High Speed (74H) - 50 MHz

(74S) - 125 MHz

É importante observar que para os flip-flops TTL é preciso alguns cuidados, como por exemplo, manter sempre as entradas CLEAR e PRESET em níveis definidos. Deixando estas entradas abertas, podem ocorrer instabilidades de funcionamento.

O nível em que elas devem ser deixadas, ou seja, sua conexão no Vcc ou 0 V depende da aplicação.a) 7473 - DUPLO FLIP-FLOP J-K COM CLEAR

Num único invólucro de 14 pinos Dual in Line temos 2 flip-flops do tipo J-K com entrada de Clear. A pinagem deste circuito integrado é mostrada na figura 1.

Os flip-flops são sensíveis ao nível de clock (Level Triggered) com entrada de Clear assíncrono. O funcionamento dos flip-flops deste circuito integrado pode ser melhor entendido pela tabela verdade da figura 2.

Nesta tabela, o símbolo com a forma de um pulso de sinal representa um pulso de clock positivo aplicado à entrada correspondente.

Observe que quando J e K estão aterradas, o clock não tem efeito sobre o circuito. Na operação normal, a entrada Clear deve ser mantida no nível alto. Se a entrada Clear for aterrada, o flip-flop resseta. A frequência máxima de operação destes flip-flops é de 20 MHz com um consumo por circuito integrado da ordem de 20 mA.b) 7474 - DUPLO FLIP-FLOP TIPO D COM PRESET E CLEAR

Os flip-flops contidos no invólucro DIL de 14 pinos disparam com a transição positiva do sinal de clock (Positive-Edge Triggered). A pinagem deste circuito integrado é mostrada na figura 3.A tabela verdade que apresenta o funcionamento dos flip-flops deste circuito integrado é dada na figura 4. Pela tabela, concluímos que a condição em que as entradas Clear e Preset estão simultaneamente ativas não deve ser usada, pois teremos uma condição não permitida para os flip-flops.

A frequência máxima de operação deste circuito integrado é de 25 MHz e o consumo é da ordem de 17 mA.c) 7475 - QUATRO LATCHES TIPO D

Os latches são como chaves que armazenam uma informação digital presente em sua entrada. A aplicação mais comum é justamente como memória, cada circuito integrado 7475 pode armazenar 4 bits de informação.Na figura 5 temos a pinagem deste circuito integrado. Quando o circuito é habilitado, o que é conseguido levando a linha “ ENABLE” ao nível alto, as saídas Q e /Q seguem a entrada D. O latch é do tipo “transparente”, logo, se as entradas forem modificadas, as saídas também se alterarão.Quando a entrada “ ENABLE” é levada ao nível baixo, as saídas não respondem aos sinais de entrada D.

Veja que o LATCH armazena a informação que estava na entrada D imediatamente antes da ocorrência de uma transição do nível alto para o nível baixo da linha de habilitação (Nível 1 para o nível 0).

O funcionamento de cada flip-flop do 7475 pode ser colocado na tabela verdade da figura 6.Este circuito integrado não serve para aplicações onde se deseja mudanças de estado a cada pulso de clock. Dizemos que este circuito não pode ser usado como um registrador de deslocamento (shift-register) que será estudado nas próximas lições.O tempo de propagação do sinal é da ordem de 24 ns e o consumo típico por circuito integrado é de 32 mA.d) 7476 - DOIS FLIP-FLOPS J-K COM PRESET E CLEAR

Os dois flip-flops deste circuito integrado têm funcionamento independente e disparam com nível do sinal de clock (level triggered).

O invólucro é DIL de 16 pinos, veja a figura 7. O funcionamento de cada um dos flip-flops pode ser melhor analisado através da tabela verdade da figura 8. Observe o símbolo adotado para representar um pulso de clock.

Da mesma forma que nos demais circuitos integrados desta série, as entradas CLEAR E PRESET devem ser mantidas em níveis lógicos definidos, para que não ocorra o funcionamento errático do circuito.Também observamos pela tabela verdade que não se pode ativar as duas entradas de CLOCK E CLEAR ao mesmo tempo, pois isso levaria os flip-flops a uma condição não permitida.Um ponto interessante que deve ser observado neste circuito integrado é a pinagem diferente, já que normalmente nos circuitos desta série a alimentação positiva é sempre nos pino 14 ou 16 e a negativa no pino 7 ou 8, quando os invólucros são de 14 ou 16 pinos. A frequência máxima de operação destes flip-flops para a série normal é de 20 MHz e o consumo de 20 mA.e) 74174 - SEIS FLIP-FLOPS TIPO D COM CLEAR

Este circuito integrado contém seis flip-flops do tipo D que são disparados na transição positiva do sinal de clock. A entrada de CLEAR é comum a todos os flip-flops. O invólucro é de 16 pinos com a identificação feita segundo mostra a figura 9.

A tabela verdade que descreve o funcionamento de cada flip-flop deste circuito integrado está na figura 10.

Observe que nestes flipflops temos acesso a apenas uma das saídas, assim, as saídas complementares não podem ser usadas.A frequência máxima dos flip-flops da série stardard (comum) é de 35 MHz com um consumo típico de 45 mA por circuito integrado.f) 74273 - OITO FLIP-FLOPS TIPO D COM CLEAR

Este circuito é semelhante ao anterior com a diferença de que existem oito em lugar de seis flip-flops tipo D. Cada um dos flip-flop pode operar com um bit, assim, esta configuração se torna ideal para aplicações em computadores, pois opera com 8 bits que correspondem a um byte.

A pinagem do circuito integrado 74273 é mostrada na figura 11.

A tabela verdade para cada flipflopé a mesma do circuito integrado anterior apresentada na figura 10.

A frequência máxima de operação para os circuitos integrados deste tipo da série normal é de 30 MHz com um

consumo de 62 mA para cada um.Veja que o invólucro usado é Dual In Line de 20 pinos e que a entrada de CLEAR é comum a todos os integrados. Também observamos que não existe acesso às saídas complementares dos flip-flops.g) 74LS373 - LATCH OCTAL TRANSPARENTE TIPO D

O tipo LS é importante neste caso, já que se trata de circuito compatível com as portas paralelas dos computadores e portanto, pode ser excitado diretamente pelos níveis lógicos existentes num PC.

Uma vez que o circuito integrado 74LS373 contém 8 latches com saída tri-state, ele pode ser usado para trabalhar com um byte inteiro, sem problemas.

A pinagem deste circuito integrado é mostrada na figura 12.

Quando a entrada /OE está no nível alto (1), as saídas de todos os flipflops vão para o estado de alta impedância. Isso significa que estas saídas podem ser ligadas a um barramento comum a outros circuitos integrados, sem o problema de conflitos que possam carregar os circuitos causando problemas de funcionamento, conforme já estudamos nas lições iniciais deste curso.

Quando a entrada /OE está ativada, o que é feito levando- a ao nível baixo (0), o estado das saídas vai depender

da entrada EL. Se EL estiver no nível alto (1), o latch estará aberto “transparente”. O que estiver na entrada D vai passar pelo circuito e aparecer na saída Q.

Se EL estiver no nível baixo (0), a saída Q não mais responde ao que ocorre nas entradas D. Nestas condições dizemos que o latch está fechado e a saída Q será o conteúdo das entradas D que foi armazenado imediatamente

antes da transição das entradas EL do nível alto para o nível baixo. Em outras palavras, podemos dizer que os flip-flops são gatilhados na transição negativa da entrada EL.Observe a condição de alta impedância obtida com /OE no nível alto. A frequência máxima de operação para os latches deste circuito integradoé de 50 MHz com um consumo de 24 mA.h) 74LS374 - OITO FLIP-FLOPS TIPO D COM SAÍDAS TRI-STATE

Temos neste circuito integrado TTL em invólucro DIL de 20 pinos 8 flipflops do tipo D que são disparados na transição positiva do sinal de clock. As saídas são tri-state e a pinagem é mostrada na figura 13.Quando a entrada /OE está no nível alto, as saídas de todos os flipflops vão para o estado de alta impedância. Veja que neste circuito integrado também não temos acessoàs saídas complementares dos flipflops. A tabela verdade que descreve o funcionamento de cada um dos flipflopsé mostrada na figura 14.A frequência máxima de operação deste circuito integrado é de 50 MHz com um consumo típico de 27 mA.2 - OS FLIP-FLOPS CMOS

Temos diversos flip-flops disponíveis na família CMOS que serão analisados a seguir. Uma recomendação importante relativa ao uso destes flipflops, assim como das demais funções CMOS, é que as entradas não usadas, pela sua sensibilidade devidaà alta impedância, nunca devem ser mantidas abertas.

Nos flip-flops CMOS, diferentemente dos TTL, as entradas assíncronas são ativadas no nível alto, o que significa que devem ser mantidas no nível baixo para a operação normal.a) 4013 - DOIS FLIP-FLOPS TIPO D COM PRESET E CLEAR

Os dois flip-flops contidos neste circuito integrado são disparados na transição positiva do sinal de clock.O invólucro é o DIL de 14 pinos da figura 15.

A tabela verdade para este circuito integrado está na figura 16.Pela tabela verdade vemos que as entradas CLEAR E PRESET são ativas no nível alto, mas que somente uma delas pode estar nesta condição de cada vez. Se as duas entradas PRESET e CLEAR forem colocadas no nível alto ao mesmo tempo, o flipflop vai para uma condição não permitida.

A informação presente na entrada D é transferida para a saída, quando as entradas assíncronas PRESET E CLEAR estão inativas.

É importante observar que a velocidade de operação dos circuitos CMOS depende da tensão de alimentação, como já estudamos nas lições anteriores.

Nos manuais de circuitos integrados CMOS os leitores poderão encontrar tabelas que trazem os diversos tempos de propagação dos sinais e as frequências de operação em função desta tensão de alimentação. Podemos dizer apenas que, para uma alimentação de 10 V, a frequência máxima de clock será de 7 MHzb) 4027 - DUPLO FLIP-FLOP J-K COM PRESET E CLEAR

Neste circuito integrado encontramos dois flip-flops tipo J-K com entradas de PRESET E CLEAR. O invólucro é DIL de 16 pinos, mostrado na figura 17.

Nos flip-flops, as entradas PRESET e CLEAR são independentes. A tabela verdade para os flip-flopsé mostrada na figura 18.Observe que temos acesso tanto as saídas normais como complementares de cada um dos flip-flops e que as saídas CLEAR E PRESET estão ativas no nível alto. No entanto, como nos demais flip-flops, estas saídas não podem ser ativadas ao mesmo tempo, pois levariam os flip-flops a uma condição não permitida.

Como no caso anterior, a frequência depende da tensão de alimentação. Para uma tensão de alimentação de 10 V, a frequência máxima de operação é da ordem de 8 MHz.c) 4043 - QUATRO FLIP-FLOPS S R-S (Lógica NOR)Este circuito integrado contém quatro flip-flops R-S independentes com saídas tri-state. O invólucro DIL de 16 pinos é mostrado na figura 19.Em cada um dos flip-flops, as entradas SET e RESET podem normalmente ficar no nível baixo. Se a entrada SET for levada ao nível alto, a saída irá e permanecerá no nível alto. Se a entrada RESET for levada ao nível alto a saída irá e permanecerá no nível baixo. As duas saídas não podem ser levadas ao mesmo tempo ao nível alto, pois isso representa um estado não permitido.

As saídas vão ao estado de alta impedância com a entrada EN (habilitação ou ENABLE) levada ao nível baixo. Quando o nível da entrada ENé alto, as saídas são conectadas aos flip-flops, transferindo seus estados para os circuitos externos.

Como estes circuitos não usam clocks, eles não devem ser ligados em cascata para formar contadores ou shift-registers.d) 40174 - SEIS FLIP-FLOPS TIPO D

Este circuito integrado contém seis flip-flops tipo D disparados pela transição positiva do sinal de clock. Apenas

uma das saídas de cada flip-flopé acessível externamente e o CLEARé comum a todos eles. O invólucro é DIL de 16 pinos com a pinagem mostrada na figura 20. Todos os flip-flops são controlados por uma entrada comum

de clock. A tabela verdade para os flip-flops deste circuito integrado é mostrada na figura 21.e) 40175 - QUATRO FLIP-FLOPS TIPO DTrata-se de um circuito integrado que contém quatro flip-flops semelhantes ao anterior com a diferença de que as duas saídas (normal e complementar) podem ser acessadas.

O invólucro deste circuito integradoé apresentado na figura 22.A tabela verdade para os circuitos integrados é a mesma do 40174. Para uma alimentação de 10 V, a frequência

máxima de clock é de 10 MHz.3 - FUNÇÕES LÓGICAS TTL

Podemos contar com uma boa quantidade de circuitos integrados contendo as principais funções lógicas em tecnologia TTL. Damos a seguir alguns dos mais importantes, já que para obter informações sobre a totalidade será interessante contar com um manual TTL.

a) 7400 - Quatro Portas NAND de duas entradas

Num invólucro DIL de 14 pinos contamos com quatro portas NAND de duas entradas de funcionamento independente.

Veja na figura 23 a pinagem deste circuito integrado.

O consumo médio por circuito integradoé da ordem de 12 mA.

b) 7402 - Quatro Portas NOR de duas entradasEste circuito integrado em invólucro DIL de 14 pinos tem a pinagem mostrada na figura 24 e cada unidade exige uma corrente de 12 mA.c) 7404 - Seis Inversores (Hex Inverter)

Os seis inversores deste circuito integrado podem ser usados de forma independente. A pinagem está na figura 25.

d) 7408 - Quatro Portas AND de duas entradasEste circuito integrado tem a pinagem da figura 26 e cada unidade exige uma corrente de 16 mA.

e) 7410 - Três portas NAND de três entradas

Cada uma das três portas NAND deste circuito integrado pode ser usada de forma independente. A corrente exigida pelo circuito é de 6 mA.

f) 7420 - Duas portas NAND de quatro entradasEste circuito integrado contém duas portas NAND que podem ser usadas de forma independente. A pinagem é mostrada na figura 28.

O consumo por unidade é de aproximadamente 4 mA.

g) 7432 - Quatro portas OR de duas entradas

As portas OR deste circuito integrado podem ser usadas de modo independente e a corrente total exigidaé da ordem de 19 mA. A pinagem está na figura 29.

h) 7486 - Quatro Portas OR-ExclusivoAs portas OU-exclusivo ou Exclusive OR deste circuito integrado podem ser usadas de forma independente. O consumo é de 30 mA e a pinagem está na figura 30.4 - FUNÇÕES LÓGICAS CMOS

Também podemos contar com uma boa quantidade de circuitos integrados CMOS contendo funções lógicas. Evidentemente, não temos espaço para colocar todas estas funções nesta lição, assim recomendamos ao leitor que adquira um manual CMOS. Daremos a seguir algumas das mais usadas.a) 4001 - Quatro Portas NOR de duas entradas

Este circuito integrado contém quatro portas NOR em invólucro DIL de 14 pinos com a pinagem mostrada na figura 31.

O consumo por circuito integradoé da ordem de 10 nW.

b) 4011 - Quatro portas NAND de duas entradas

Em invólucro DIL de 14 pinos encontramos quatro portas NOR de duas entradas de funcionamento independente. O invólucro com a identificação dos terminais é mostrado nafigura 32.

c) 4012 - Duas portas NAND de quatro entradas

As quatro portas NOR de duas entradas deste circuito integrado podem ser usadas de forma independente. A identificação dos terminais deste circuito integrado está na figura 33.d) 4023 - Três portas NAND de três entradas

As três portas NAND deste circuito integrado podem ser usadas de maneira independente. A pinagem é mostrada na figura 34.

e) 4025 - Três portas NOR de três entradas

Encontramos neste circuito integrado três funções NOR que podem ser usadas de forma independente. A pinagem é mostrada na figura 35.

5 - A FUNÇÃO TRI-STATE EXPANSÍVEL DO 4048

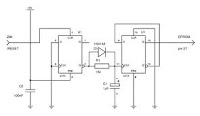

O circuito integrado 4048 tem características muito interessantes para projetos CMOS envolvendo funções lógicas. Conforme estudamos, usando combinações apropriadas de funções simples, é possível simular qualquer outra função mais complexa.É justamente isso que faz o 4048 que tem a pinagem mostrada na figura 36.

Este circuito possui 8 entradas, uma saída e três entradas de “programação”.Dependendo dos níveis lógicos aplicados nestas entradas de programação, o circuito se comporta como funções NOR, OR, NAND ou AND com 8 entradas ou ainda de forma combinada, realizando ao mesmo tempo funções de portas OR e AND cada um de 4 entradas e outras que são mostradas na figura 37.

Assim, por exemplo, se colocarmos todas as três entradas de programação no nível alto (Ka,Kb e Kc= 111), o circuito se comporta como duas portas AND de quatro entradas ligadas a uma porta OR de duas entradas.

Veja então que esta interessante função pode servir de “coringa” em muitos projetos, pois consegue simular a operação de diversas combinações de outros circuitos integrados CMOS.

Internamente, o 4048 é bastante complexo contendo 32 funções independentes programadas pelos níveis lógicos aplicados às entradas correspondentes.

Blog destinado aos profissionais,estudantes, hobistas... ou seja, todos os amantes da eletrônica e eletricidade

02 março 2012

Os flip-flops e funções lógicas em circuitos integrados

Assinar:

Postar comentários (Atom)

Nenhum comentário:

Postar um comentário